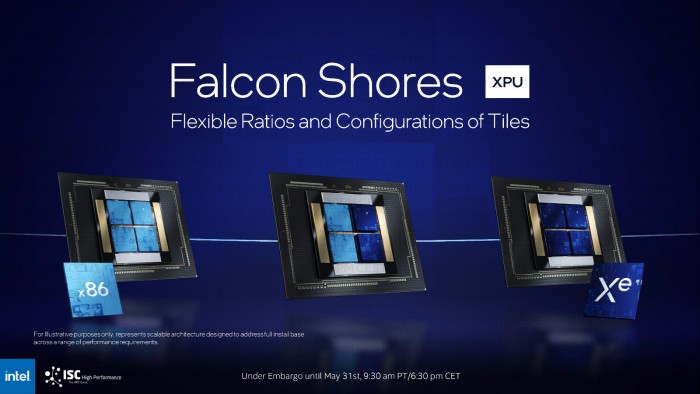

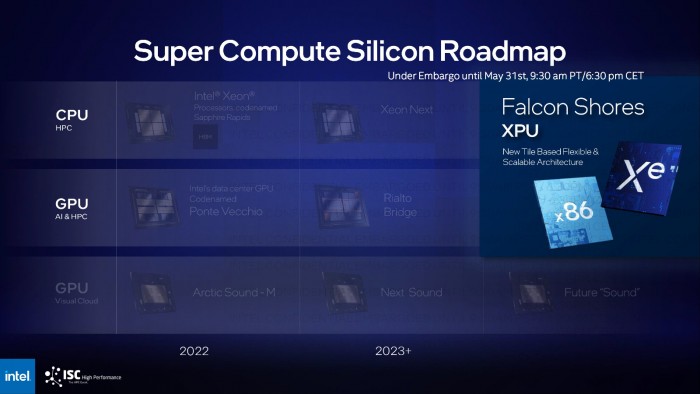

今年早些时候,英特尔公布了 Falcon Shores XPU 产品线。作为一种新颖的可扩展芯片设计,其旨在利用 x86 与 Xe 内核来处理超算工作负载。在周二的 ISC 2022 大会上,英特尔披露了基于至强(Xeon)平台的 Falcon Shores 芯片的更多配置细节。可知 XPU 架构不是简单的 CPU + GPU 组合,而是集成了几项全新的技术,使之能够在其它几个领域脱颖而出。

看到 XPU 的第一眼,很多人可能马上联想到了 AMD 已经研究了有段时间的 Exascale APU —— 预计于明年某个时候推出的 Instinct MI300 解决方案,就将 Zen CPU 内核与 CDNA 小芯片结合到了一起。

展望未来,Falcon Shores 是英特尔芯片路线图中的下一个主要架构创新,它将 x86 CPU 和 Xe GPU 架构整合到了一个插槽之中。

英特尔希望到 2024 年的时候,带来超过 5 倍的性能功耗比、计算密度、存储容量、以及带宽等方面的优势改进。

英特尔还将 Falcon Shores XPU 称作“基于小瓦片的新颖灵活且可扩展架构”,意味着无论是 CPU、GPU、还是 XPU,小瓦片(Tiles)都将成为 Intel 下一代芯片的基本组成部分。

该公司在 ISC 2022 大会上展示了三种配置(仅用于说明目的),包括一套完整的 x86 瓦片、一套 Xe GPU 瓦片、以及一套同时使用 x86 CPU + Xe GPU 内核的解决方案。

三种配置的侧重点不尽相同,但所有设计的共通点是它们都具有至少四个瓦片 —— 布局类似于英特尔的 Sapphire Rapids 至强 CPU 产品线。

虽然 Intel 尚未提到基于高带宽缓存(HBM)的解决方案,但我们也不排除后续有升级型号出现的可能。

以下是 Falcon Shores XPU 可带来的一些亮点:

● 灵活的 x86 与 Xe 瓦片设计比例

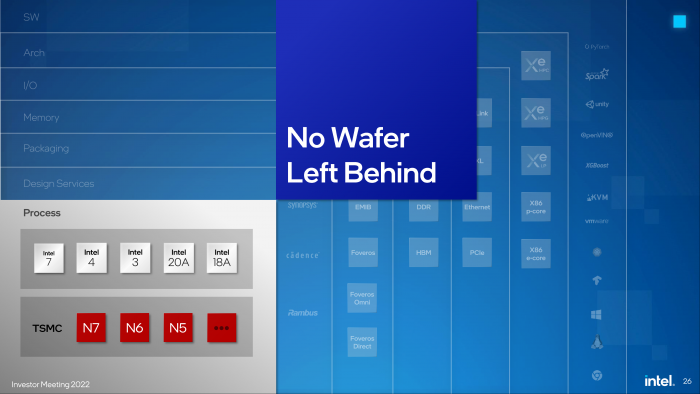

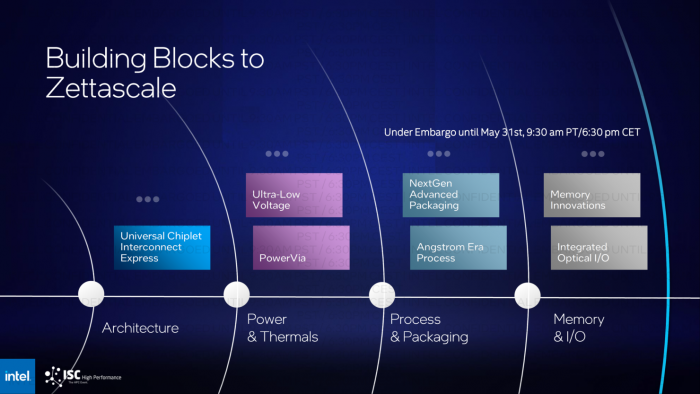

● 向埃(Angstrom)级制程迈进

● 超高的共享缓存带宽

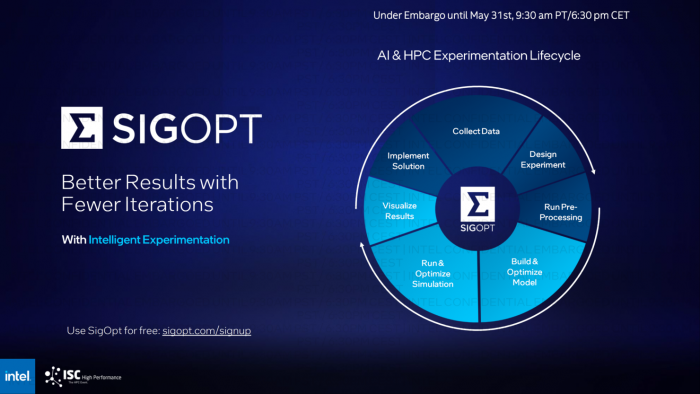

● 简化的编程模型

● 下一代先进封装工艺

● 业内领先的 I/O

鉴于英特尔已经提到过“埃”(1A = 0.1nm)级工艺节点,我们推测 Falcon Shores XPU 或基于 20A 或 18A 制程。

根据英特尔的路线图,这款 XPU 预计在 2024-2025 年前后推出,且该公司或提供基于 HBM 高带宽缓存的选项。

此外与标准单芯片设计相比,Falcon Shores XPU 还会用上更加复杂的下一代先进封装(比如 EMIB / Foveros 的迭代版本)。

英特尔分享的 Falcon Shores XPU 设计的初步性能优势如下:

● 超 5 倍的每瓦特性能改进

● 为 x86 插槽带来超 5 倍的计算密度提升

● 提供超五倍的内存容量 / 带宽支持

需要指出的是,上述性能目标仅针对 2022 年 2 月已有的平台而预估得出。

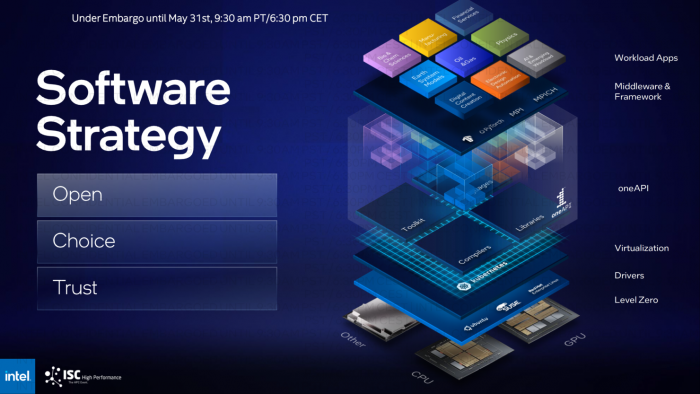

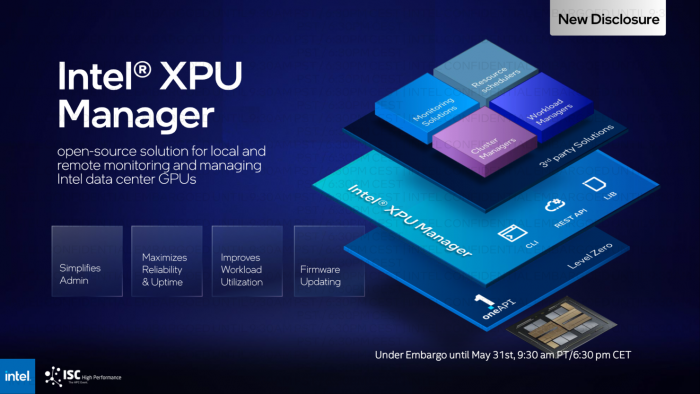

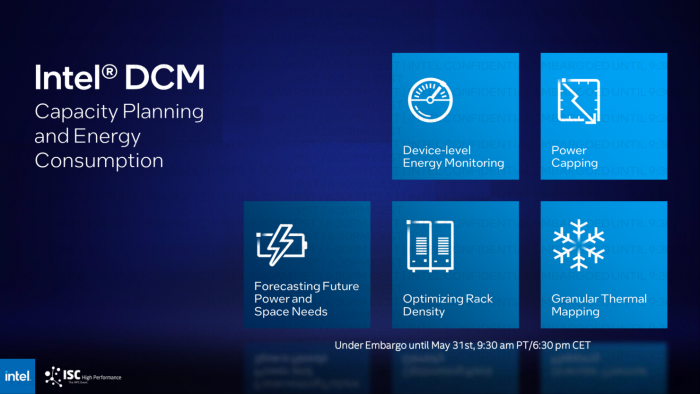

另外整个英特尔 Falcon Shores XPU 平台将围绕 oneAPI 软件套件予以调整,为数据中心级芯片的本地 / 远程监控和管理提供开源解决方案。

最后,鉴于 Falcon Shores XPU 产品线仍处于早期开发阶段,该公司显然还会在即将到来的活动中披露更多细节。