近日,华硕电脑中国区负责人俞元麟,通过其B站账号“普普通通Tony大叔”,分享了一段由B站用户万扯淡与kurnal共同制作的深度解析视频,内容聚焦于AMD最新推出的锐龙AI Max+ 395 "Strix Halo"处理器芯片的内部结构。

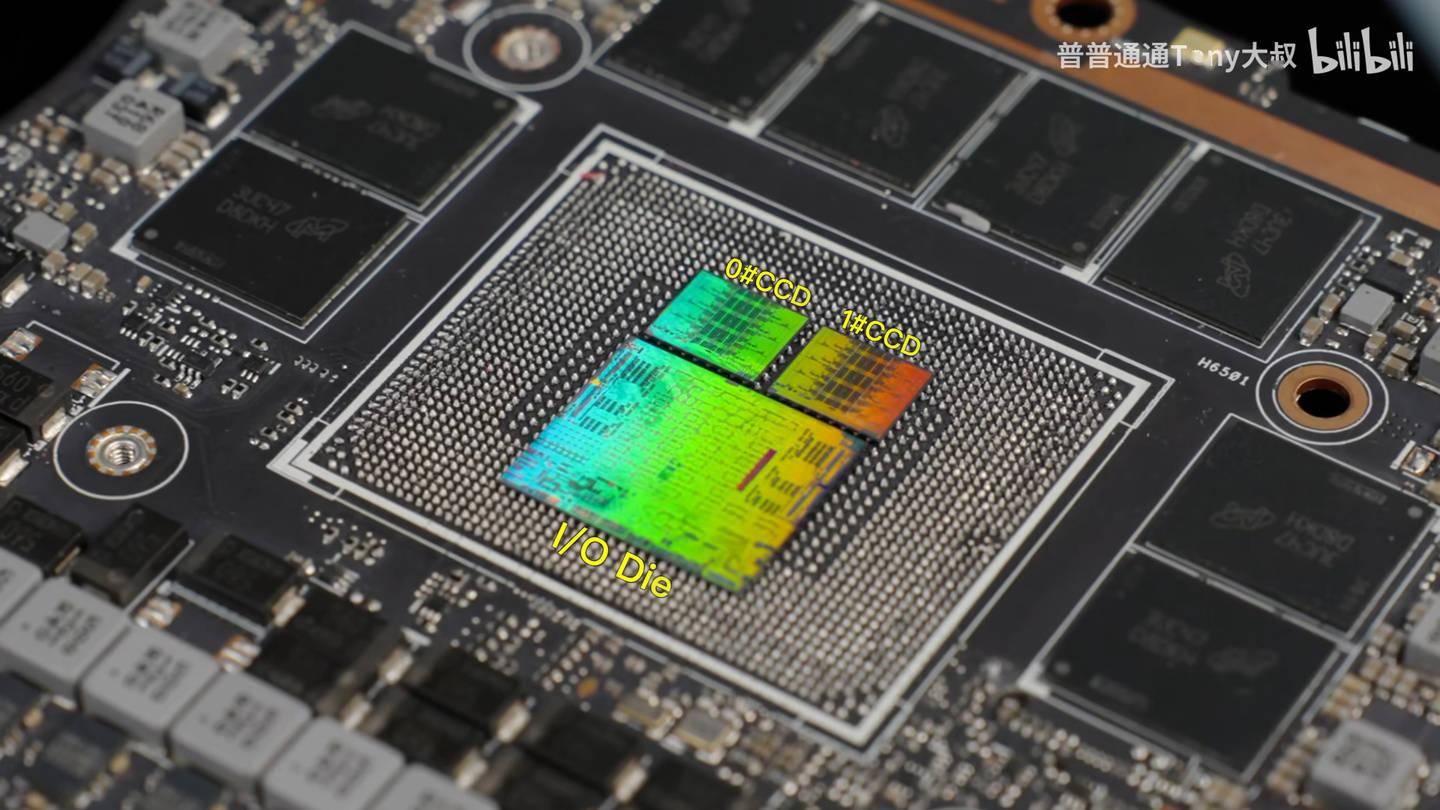

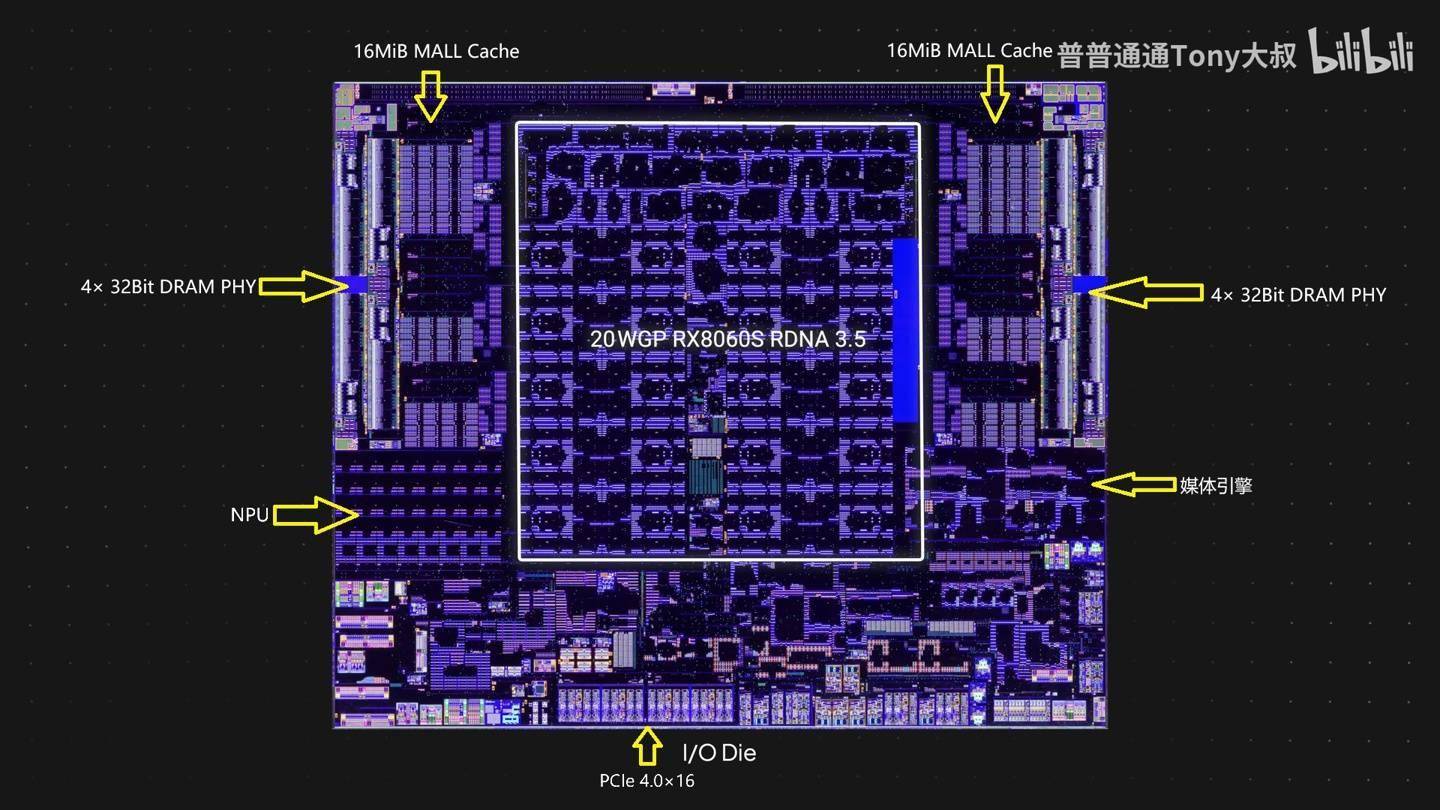

据视频揭示,AMD在打造这款"Strix Halo"处理器时,采用了两颗台积电4nm制程的CCD芯片,每颗芯片面积约为67.07平方毫米,并搭配了一颗同样采用4nm制程的IOD芯片,其面积更是达到了307.584平方毫米。尤为引人注目的是,IOD芯片内嵌入了拥有20个WGP(工作组处理器)的超大规模核心显卡。

在CCD部分,AMD借鉴了桌面端锐龙9000 "Granite Ridge"处理器的核心设计,因此"Strix Halo"芯片得以保留专为3D V-Cache集成设计的TSV接口引脚。这一设计策略不仅确保了性能上的连续性,也为未来可能的性能升级预留了空间。

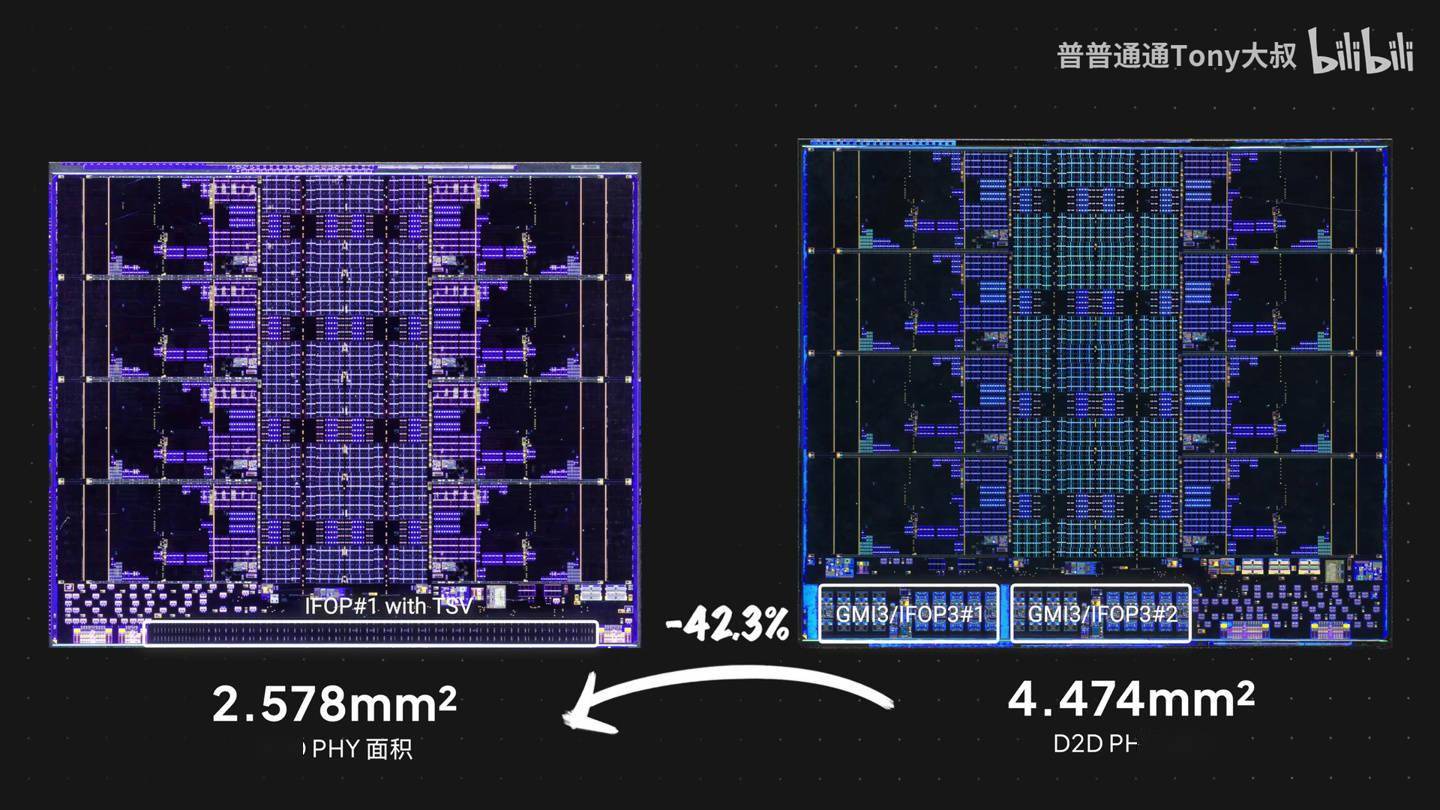

不过,AMD并未止步于简单的复用,而是对CCD的边缘I/O进行了创新性的调整。他们放弃了传统的基于SerDes的互联方式,转而采用了水平扇出封装技术。这一变革使得"Strix Halo"所用的CCD在纵向上缩减了0.34毫米,互联区域面积更是减少了42.3%,从而实现了更为紧凑和高效的芯片布局。

IOD部分同样亮点纷呈。其中心区域被两片大型RDNA 3.5核心显卡占据,左右两侧则分布着两片16MiB的MALL Cache(即Infinity Cache)。而靠近边缘的位置,则整齐排列着8组共256bit的DRAM内存接口,为数据的快速传输提供了有力保障。

"Strix Halo"的IOD下方还集成了包括NPU(神经处理单元)、媒体引擎以及PCIe接口在内的一系列复杂电路,这些组件的协同工作,使得这款处理器在数据处理、图形渲染以及多媒体应用等方面均展现出了卓越的性能。