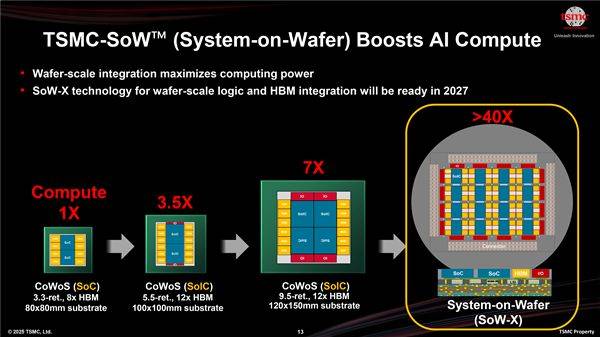

在高端计算芯片领域,规模的不断扩大已成为一种趋势,而台积电正积极应对这一挑战,全力推进其CoWoS封装技术的发展。据最新消息,该公司正致力于打造一种前所未有的巨型芯片,其面积将接近8000平方毫米,功耗可达1000W,性能更是标准处理器的40倍之多。

目前,台积电的CoWoS封装技术已经能够实现中介层面积达到2831平方毫米,这一尺寸已经远远超过了其EUV极紫外光刻光罩的极限尺寸830平方毫米,达到了大约3.3倍的水平。这种封装技术被广泛应用于NVIDIA B200、AMD MI300X等芯片中,通过整合大型计算模块和多个HBM内存芯片,实现了出色的性能表现。

然而,台积电并未止步于此。据透露,该公司计划在明年或稍晚些时候推出下一代CoWoS-L封装技术,中介层面积将进一步扩大至4719平方毫米,达到光罩极限尺寸的约5.5倍。该技术还需要使用10000平方毫米的大型基板,以支持更多组件的整合。据称,下一代CoWoS-L封装技术将能够整合最多12颗HBM内存,包括即将推出的HBM4。

不仅如此,台积电还有更大的野心。他们计划将中介层面积进一步扩大至7885平方毫米,这一尺寸已经是光照极限尺寸的约9.5倍。为了实现这一目标,他们将需要使用18000平方毫米的基板,并封装最多4颗计算芯片、12颗HBM内存以及其他IP。这一尺寸甚至已经超过了一个标准的CD光盘盒的大小。

随着芯片尺寸的增大,功耗和散热问题也日益凸显。台积电预计,这些巨型芯片的功耗将达到1000W级别。为了解决这一问题,台积电计划在CoWoS-L封装内的RDL中介层上直接集成一整颗电源管理IC。这颗IC将使用台积电的N16工艺和TSV硅通孔技术制造,旨在缩短供电距离、减少有源IC数量、降低寄生电阻并改进系统级供电效率。

在散热方面,台积电也在积极寻求解决方案。直触式液冷和浸没式液冷等技术都被认为是可行的选项。随着OAM 2.0模块形态的发展,100×100毫米的基板已经接近其极限尺寸。因此,台积电也在呼吁行业同步制定新的OAM形态标准,以适应更大尺寸的芯片封装需求。